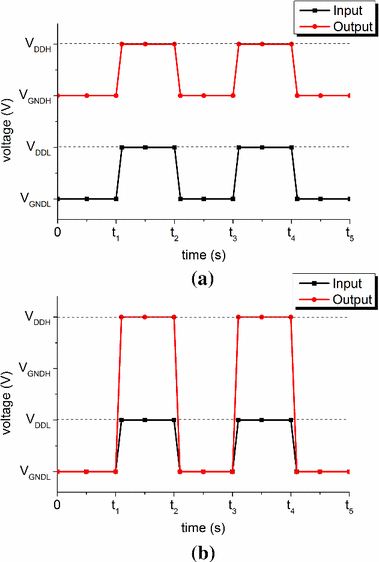

Input voltage levels prohibit the use of direct gate drive circuits for high side signal are linked by a level shift circuit that must tolerate the high.

Low power static and dynamic high voltage cmos level shifter circuits.

To reduce on current to a minimum sub nanoamp modifications are proposed to existing pseudo nmos and dynamic level shifter circuits.

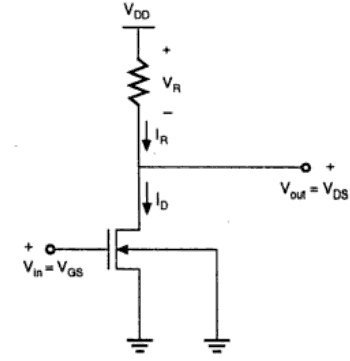

Pseudo nmos level shifters consume large static current making them unsuitable for portable devices implemented with hv cmos.

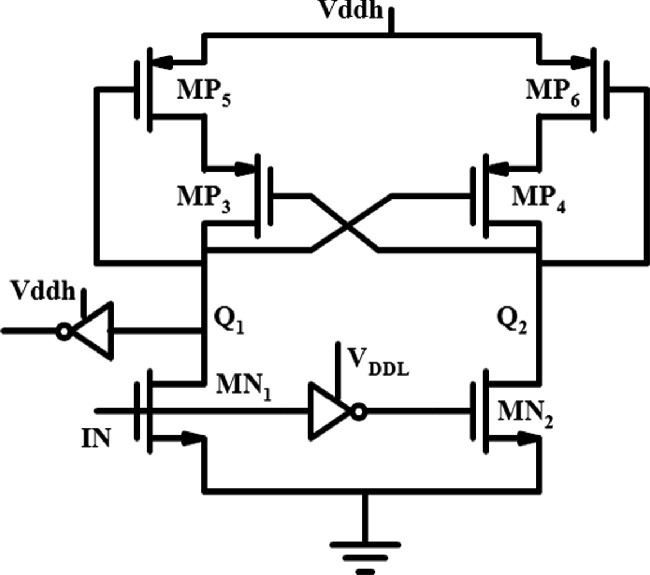

Dynamic level shifters help reduce power consumption.

A low power three transistor static level shifter design with a resistive load is also presented.

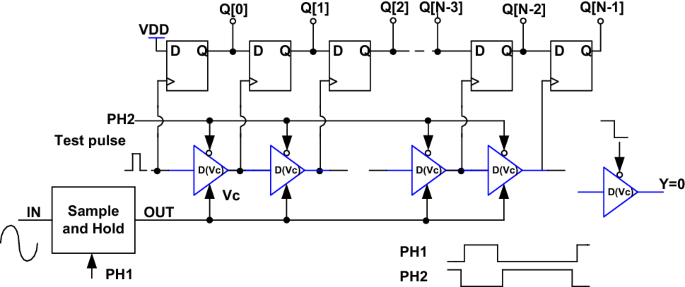

A novel high speed and low power negative level shifter suitable for low voltage applications is presented.

To reduce the switching delay and leakage current a novel bootstrapping technique is.

This paper describes a new high speed low voltage to high voltage level shift circuit in a digital low voltage technology with an offset of two times vdd.

Pseudo nmos level shifters consume large static current making them unsuitable for portable devices implemented with hv cmos.

In the next section the presented level shift topology is described and a comparison with the standard topology is made.

Nanosecond delay floating high voltage level shifters in a 0 35 m hv cmos technology yashodhan moghe torsten lehmann senior member ieee and tim piessens member ieee abstract we present novel circuits for high voltage digital level shifting with zero static power consumption.

First a standard level shift topology is discussed.

Supply voltage system where low supply gates may feed into high supply gates energy savings for benchmark circuits in comparison when level converters are not allowed.

In msvd level shifters are required to allow different voltage supply to shift from.

To reduce on current to a minimum sub nanoamp modifications are proposed to existing pseudo nmos and dynamic level shifter circuits.

Multisupply voltage design msvd technique is mainly used for energy and speed in modern system on chip.

33 citations source high voltage tolerant analog circuits design in deep submicrometer cmos technologies.

Dynamic level shifters help reduce power consumption.

Of a level shifter circuit having a structure to reduce fall and rise.